# **BARREL SHIFTER**

A miniproject report submitted in partial fulfillment of the requirements for the award of the degree of

## **BACHELOR OF TECHNOLOGY**

#### IN

## **ELECTRONICS & COMMUNICATION ENGINEERING**

**Submitted by**

| P. Sumanth Kumar | (08R01A04B2) |

|------------------|--------------|

| P. Kishore Kumar | (08R01A04B3) |

| Y. Anji Reddy    | (08R01A04C7) |

**Under The Esteemed Guidance Of**

Asst. Professor N.V. Rama Krishna.

#### **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

CMR INSTITUTE OF TECHNOLOGY (AFFILIATED TO JAWAHERLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD) (AN ISO 9001:2000 CERTIFIED ISTITUTION) KANDLAKOYA, MEDCHAL ROAD, HYDERABAD - 501401.

2011 - 2012

## **CERTIFICATE**

#### **CMR INSTITUTE OF TECHNOLOGY**

This is to certify that the miniproject work entitled "BARREL SHIFTER" is a bonafide work carried out by the student in partial fulfillment of the requirements for the degree of BACHELOR OF TECHNOLOGY in ELECTRONICS & COMMUNICATION ENGINEERING During the academic year 2011-2012.

P. Sumanth Kumar P. Kishore Kumar Y. Anji Reddy (08R01A04B2) (08R01A04B3) (08R01A04C7)

(N.V. Rama Krishna) Asst. Professor Internal guide (Prof. A. Balaji Nehru) Head of the department Electronics & Communication Engineering

**External examiner**

## **DECLARATION**

We hereby declare that the results embodied in this Dissertation entitled "**BARREL SHIFTER**" is carried out by us for the partial fulfillment of the project requirements for the award of degree.

We have not submitted to any other University /Institute for the award of any degree.

| P. Sumanth Kumar | (08R01A04B2) |

|------------------|--------------|

| P. Kishore Kumar | (08R01A04B3) |

| Y. Anji Reddy    | (08R01A04C7) |

## **CERTIFICATE**

This is to certify that the Dissertation entitled "**BARREL SHIFTER**" is a bonafide work done by Y. Anji Reddy(Roll No: 08R01A04C7), P. Sumanth Kumar (Roll No: 08R01A04B2), P. Kishore Kumar(RollNo:08R01A04B3) final year students of B.Tech (ECE), in partial fulfillment of the requirements for the award of the degree of Bachelor Of Technology in Electronics & Communication Engineering, submitted to the Department of Electronics and Communication Engineering, CMR INSTITUTE OF TECHNOLOGY, Hyderabad. The Project work has been carried out at CMR INSTITUTE OF TECHNOLOGY, Hyderabad under my supervision and guidance.

**DATE:**

SIGNATURE

(Head of the department)

**External Examiner**

## **ACKNOWLEDGEMENT**

The satisfaction that accompanies the successful completion of any task would be incomplete without a mention of the people, who made it possible and whose guidance and encouragement crown all the efforts with success. i would like to take this opportunity to express my deep sense of gratitude and extend my best wishes to all the people who have guided inspired and motivated me during this project and given me immense pleasure to acknowledge their cooperation.

I offer my sincere thanks to **Mr. N.V. Rama Krishna** project guide for readily responding to the request to do the project at **CMR INSTITUTE OF TECHNOLOGY**, Hyderabad. I highly indebted to him, who was not only shown atmost patience, but fertile in suggestions vigilant in the directions of error and who has infinitley helpful.

I express my deep sense of gratitude **to Asso. Prof. N.V.Rama Krishna**, project internal guide for her help, through provoking discussions invigorating suggestions extended to me with immense care zeal throughout the work. I am also thankful for her interminable help in overcoming all hurdles in flow of my project.

I am thankful to **Prof. A. BALAJI NEHRU**, Head of the department ECE for his constant source of encouragement and inspiration for me to strive hard and give my best to anything undertaken.

No small amount of gratitude would be sufficient to **Dr. M. JANGA REDDY**, principal, CMR institute of technology, for his kind encouragement.

| P. Sumanth Kumar | (08R01A04B2) |

|------------------|--------------|

| P. Kishore Kumar | (08R01A04B3) |

| Y. Anji Reddy    | (08R01A04C7) |

# LIST OF CONTENTS

## TOPICS

| CHAPTER 1: | INTRODUCTION                                  | 1  |

|------------|-----------------------------------------------|----|

| CHAPTER 2: | FUNCTION OF BARREL SHIFTER                    |    |

|            | 2.1 Architecture                              | 2  |

|            | 2.2 Gate type                                 | 3  |

|            | 2.3 Right rotate                              | 4  |

|            | 2.4 Left rotate                               | 4  |

|            | 2.5 Right shift                               | 5  |

|            | 2.6 Left shift                                | 5  |

|            | 2.7 Applications                              | 7  |

|            |                                               |    |

| CHAPTER 3: | AN INTRODUCTION TO XLIX 9.1i                  |    |

|            | 3.1 Getting started                           | 11 |

|            | 3.2 Create a new project                      | 13 |

|            | 3.3 Create an HDL source                      | 15 |

|            | 3.4 Design simulation                         | 21 |

|            | 3.5 Simulating design functionality           | 24 |

|            | 3.6 Create timing constraints                 | 25 |

|            | 3.6.1 Entering timing constraints             | 26 |

|            | 3.6.2 Implement design and verify constraints | 27 |

|            | 3.6.3 Download design to the spartan 3E-kit   | 30 |

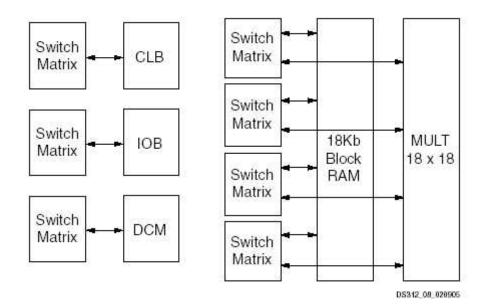

## CHAPTER 4: INTRODUCTION TO FPGA

| 4.1 Introduction                                      | 31 |

|-------------------------------------------------------|----|

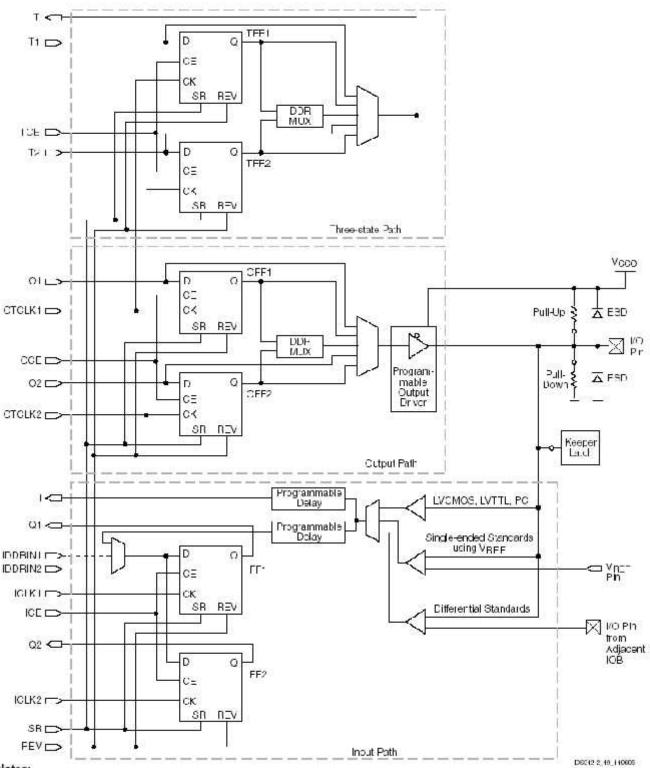

| 4.2 Input/output blocks                               | 34 |

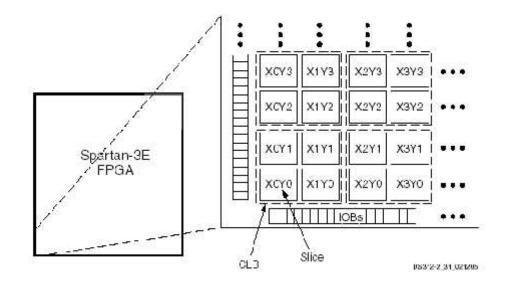

| 4.3 Configurable logic block(CLB) and slice resources | 37 |

| 4.4 Interconnect                                      | 44 |

| 4.5 Overview                                          | 44 |

## CHAPTER 5: INTRODUCTION TO SPARTAN 3E- Kit

|            | 5.1 Introduction                                   | 45 |

|------------|----------------------------------------------------|----|

|            | 5.2 Board power                                    | 46 |

|            | 5.3 Configuration                                  | 47 |

|            | 5.4 Oscillators                                    | 48 |

|            | 5.5 User input                                     | 48 |

|            | 5.6 PS/2 Port                                      | 49 |

|            | 5.7 Dumping Procedure and programming through JTAG | 49 |

|            |                                                    |    |

| CHAPTER 6: | RESULTS                                            | 52 |

|            |                                                    |    |

| CHAPTER 7: | CONCLUSION                                         | 58 |

|            |                                                    |    |

| CHAPTER 8: | FUTURE SCOPE                                       | 58 |

|            |                                                    |    |

| CHAPTER 9: | REFERENCES | 58 |

|------------|------------|----|

|            |            |    |

# **LIST OF FIGURES**

| S.no | Fig. Name                                 | Page. No |

|------|-------------------------------------------|----------|

| 1.   | Structure of an array shifter             | 2        |

| 2.   | Structure of a log shifter                | 3        |

| 3.   | ISE Help topics                           | 12       |

| 4.   | New project wizard and help topics        | 14       |

| 5.   | Define module                             | 16       |

| 6.   | New project ISE                           | 17       |

| 7.   | Initial timings                           | 22       |

| 8.   | Behavioral simulation section             | 24       |

| 9.   | Simulation result                         | 25       |

| 10.  | Prompt to add UCF file to project         | 26       |

| 11.  | Post implementation design                | 27       |

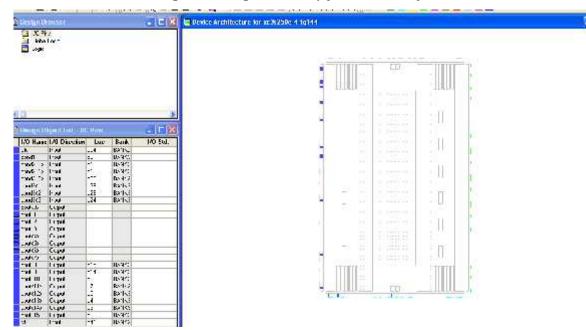

| 12.  | Package pin location                      | 29       |

| 13.  | iMPACT welcome dialog box                 | 31       |

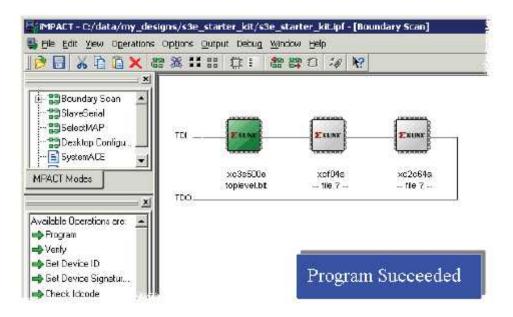

| 14.  | Boundary scan                             | 32       |

| 15.  | Simplified IOB diagram                    | 36       |

| 16.  | CLB array location                        | 38       |

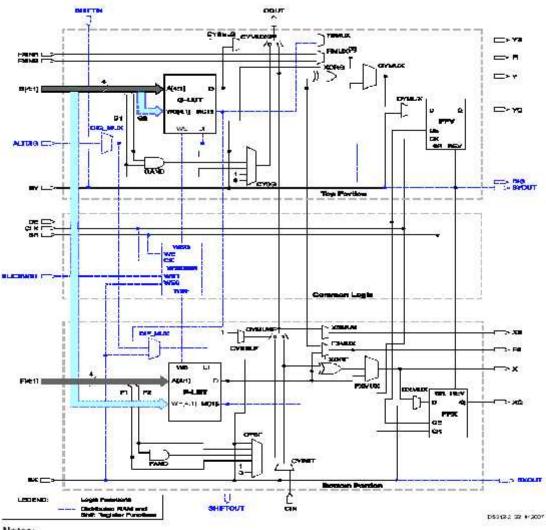

| 17.  | Amplified diagram of the left hand SLICEM | 40       |

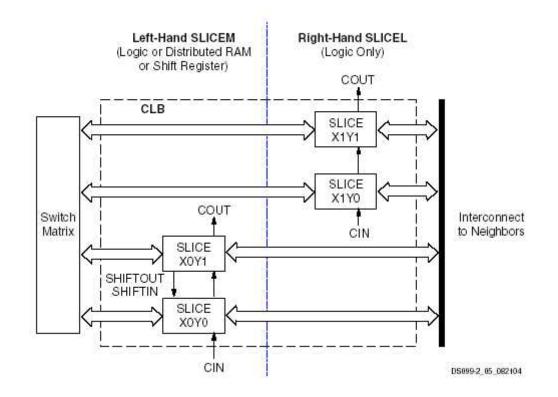

| 18.  | Arrangement of slices within the CLB      | 41       |

| 19.  | Resources in CLB                          | 41       |

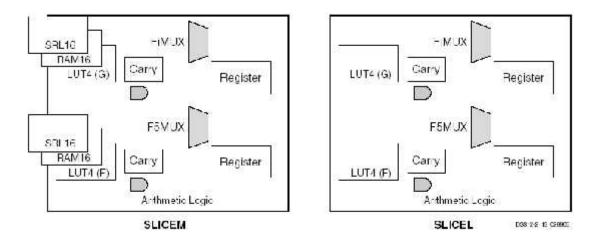

| 20.  | Resources in slices                       | 42       |

| 21.  | Four types of interconnect tiles          | 44       |

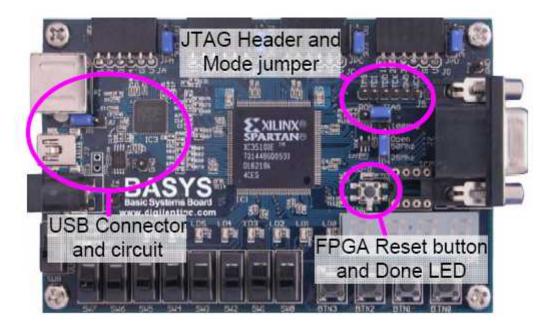

| 22.  | Basys programming circuit locations       | 46       |

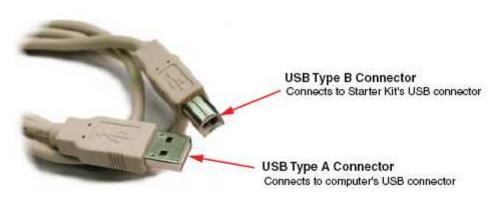

| 23.  | Standard USB type A/ type B cable         | 49       |

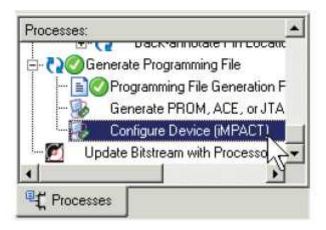

| 24.  | To invoke iMPACT procedure                | 50       |

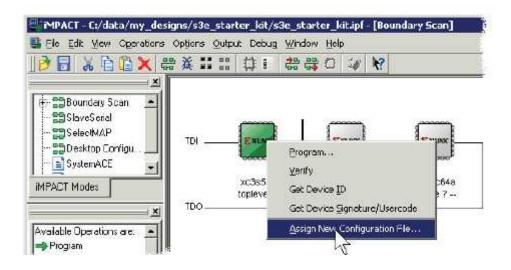

| 25.  | Assigning a configuration file to FPGA    | 51       |

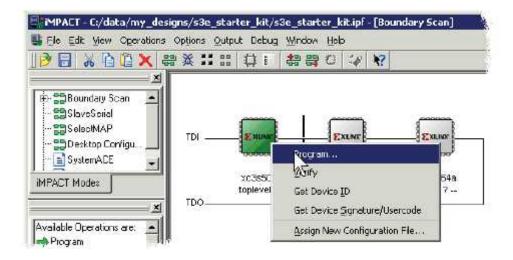

| 26.  | iMPACT for startup clock CCLK             | 51       |

| 27. | Window to program Spartan3E FPGA           | 52 |

|-----|--------------------------------------------|----|

| 28. | Simulation result for left shift           | 53 |

| 29. | Simulation result for right shift          | 54 |

| 30. | Simulation result for circular left shift  | 54 |

| 31. | Simulation result for circular right shift | 55 |

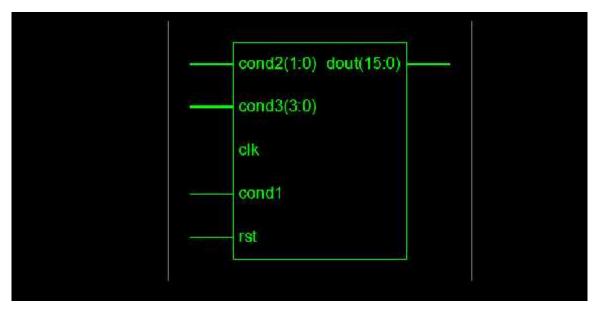

| 32. | Block diagram of barrel shifter            | 55 |

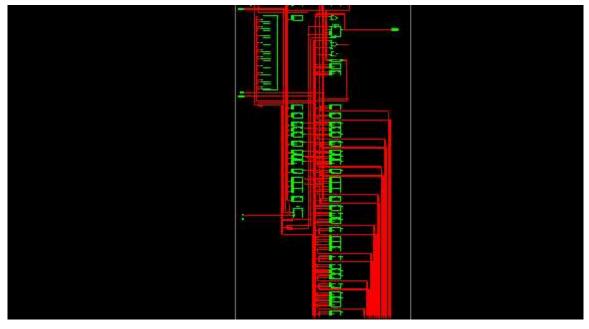

| 33. | Register transfer logic for barrel shifter | 56 |

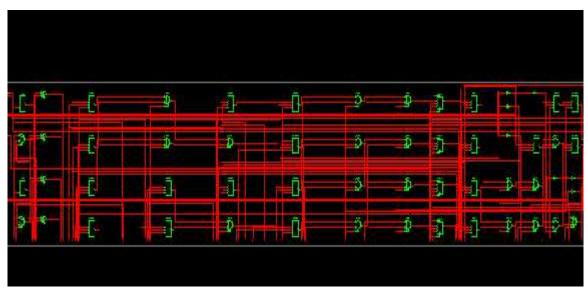

| 34. | Technology schematic                       | 56 |

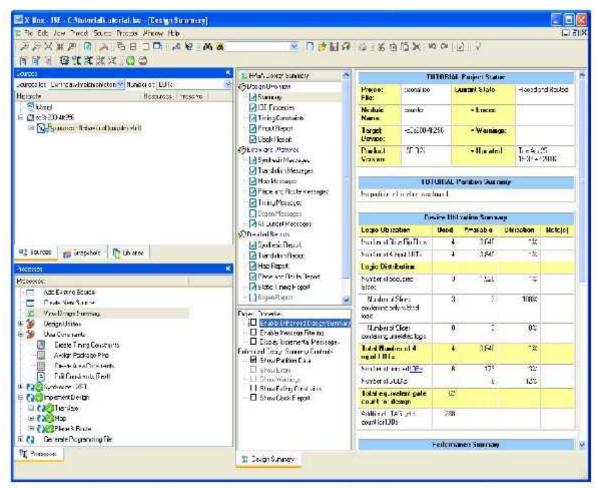

| 35. | Design summary for barrel shifter          | 57 |

| 36. | Pin assignment for barrel shifter          | 57 |

## <u>CHAPTER – 1</u> INTRODUCTION

#### **1.1 Introduction**

A barrel shifter is a digital circuit that can shift a data word by a specified number of bits. It can be implemented as a sequence of multiplexers. In this implementation, the output of one MUX is connected to the input of the next MUX in a way that depends on the shift distance. The number of multiplexers required is  $n*\log_2(n)$ , for an *n* bit word. Four common word sizes and the number of multiplexers needed are listed below:

- $64\text{-bit} 64 * \log_2(64) = 64 * 6 = 384$

- $32\text{-bit} 32 * \log_2(32) = 32 * 5 = 160$

- $16\text{-bit} 16 * \log_2(16) = 16 * 4 = 64$

- 8-bit  $8 * \log_2(8) = 8 * 3 = 24$

Basically, a barrel shifter works to shift data by incremental stages which avoids extra clocks to the register and reduces the time spent shifting or rotating data (the specified number of bits are moved/shifted/rotated the desired number of bit positions in a single clock cycle). A barrel shifter is commonly used in computer-intensive applications, such as Digital Signal Processing (DSP), and is useful for most applications that shift data left or right - a normal style for C programming code.

Rotation (right) is similar to shifting in that it moves bits to the left. With rotation, however, bits which "fall off" the left side get tacked back on the right side as lower order bits, while in shifting the empty space in the lower order bits after shifting is filled with zeros.

Data shifting is required in many key computer operations from address decoding to computer arithmetic. Full barrel shifters are often on the critical path, which has led most research to be directed toward speed optimizations. With the advent of mobile computing, power has become as important as speed for circuit designs. In this project we present a range of 32-bit barrel shifters that vary at the gate, architecture, and environment levels.

## <u>CHAPTER – 2</u> <u>FUNCTION OF BARREL SHIFTER</u>

Each shifter will be designed as a 16-bit shifter that receives a 16-bit input data value along with a two's compliment encoded shift value, and will produce a 16- bit shifted result. This section will describe the internal design characteristics for each shifter.

## 2.1 Architecture

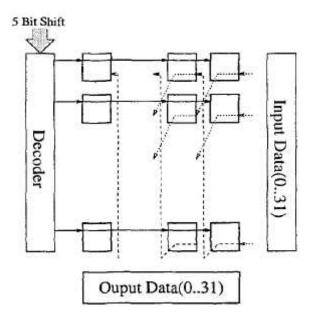

There are two common architectural layouts for shifts, array shifter and logarithmic shifters. An array shifter(Fig. 1) decodes the shift value into individual shift bit lines that mesh across all input data values. At each crossing point, a gate will either allow or not allow the input data value to pass to the output line, controlled by a shift bit line. The advantage of this design is that there is only ever one gate between the input data lines and the output data lines, so it is fast. The disadvantages of this design are the requirement for a decoder, and the fact that each input data line sees a load from every shift bit line.

Fig. 1: Structure of an array shifter.

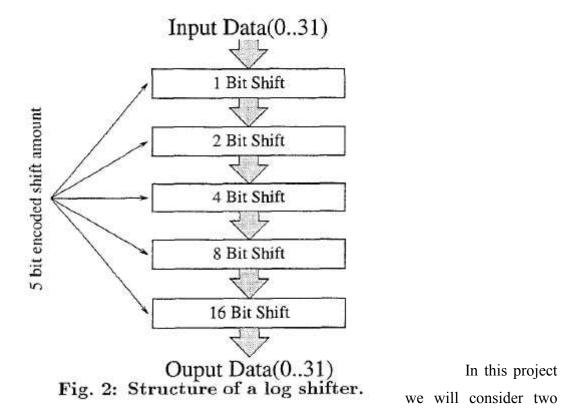

In a logarithmic shifter (Fig. 2), the shifter is divided into loga(n) stages, where *n* is the input data length. Each bit of the encoded shift value is sent to a different stage of the shifter. Each stage handles a single, powerof- two shift. The input data will be shifted or not shifted by each of the stages in sequence. Five stages would be required when considering **32** bit data. The advantage of a log shifter is that it has small area and does not require a decoder, but the disadvantage is that there are five levels of gates separating the input data from the output data.

### 2.2 Gate Type

There are two types of gates that are required for these shifters: the array shifter requires switches that will either propagate or not propagate an input data bit, and the log shifter requires 2-to-1 muxes to propagate either a shifted or a non-shifted bit.

types of CMOS switches: (1) ntype pass transistor switch; and (2) a full transmission gate switch; and we will consider four types of mux designs: (1) n-type pass transistor mux; (2) full transmission mux;

(3) a static CMOS mux; and (4) a dynamic logic mux. The pass transistor and transmission gates are simple and fast, but will require occasional buffering to strengthen the signals in the log shifters. The static and dynamic gates are self buffering so no additional buffers are needed, but contain more transistors. The dynamic gate design is the only type that requires a clock signal for a precharge stage. Figure **3** shows schematics for each gate design.

#### 2.3 Right Rotation

Right rotation is similar to right shifting, except that additional hardware is required to determine which values get shifted into the upper bits of the output. We consider three options: (1) a wrap around least significant bit for right rotation; (2) a sign bit for arithmetic right shifting; and (3) *GND* for signed magnitude right shifting. **A** 3-to-1 control mux was added to each wrap around bit line. This mux allows either the rotation wrap-around bit, the sign bit, or *GND* to be selected.

#### 2.4 Left Rotation

Left rotations can be accomplished by rotating right 32 - *Rotatereft* bits. *Rotate,i,ht* can be calculated by taking the two's-compliment of the *Rotateleft* value, which requires inverting all the *Rotateleft* bits and adding one. The inversion of the *Rotateleft* bits can be accomplished by adding muxes that pass either the shift bit or its inverse. The addition of one to *Rotateleft* can be accomplished in two ways: (1) include a 5 bit incrementor; or (2) add an additional one-bit shift stage.

#### 2.5 Left Shifting

Left shifting can be performed by right shifting 16 - Shift left bits, and including an additional row of pull down gates that mask out the lower *n* bits of the *n* bit left shift. A second method is to initially reverse the input data bits and perform a right shift of length *Shiftleft*, and finally reverse the output bits.

## 2.6 Applications

- Digital Signal Processing

- Array Processing

- Graphics

- Database Addressing

- High Speed Arithmetic Processors

## **Role of barrel shifter in DSP**

In digital signal processing (DSP) chips used in processors, a very large number of mathematical operations, including multiplications and additions, need to be performed at high speed. To accomplish this, high speed data path components are required on the DSP chip.

A DSP chip that performs arithmetic operations is a math processor. This processor is coupled to a system bus to receive and send data over the bus to other components in the computer system. An ALU (Arithmetic Logic Unit) is one of the main components that performs arithmetic operations in the math processor within the DSP chip. In order to improve the performance of the ALU, data is often manipulated prior to its introduction into the ALU. For example, from the system bus, incoming data can be normalized by a right shifter that scales down the magnitude of the number represented by the incoming data to make the number more manageable for later operations performed by the ALU. The ALU will then perform the required operation, such as addition, logical AND/OR and EX-OR functions, on the shifted data.

The result of the ALU operation is provided to a left shift device which shifts the ALU result to the left. This has the effect of scaling the number by a proper amount to restore normalization. The re-normalized result of the ALU operation is then placed on the system bus.

One type of shifter used in digital signal processing applications is a barrel shifter that will shift a plurality of bits in a single clock cycle. Barrel shifters are particularly advantageous in high performance applications in comparison to serial shifters which would require N clock cycles to shift a number by N bits. A barrel shifter forms a high-speed data path component that is very useful in high-performance applications.

A design goal of a DSP chip designer is to provide the requisite high performance while reducing its power consumption. Power consumption is problematical in barrel shifters since data passes through the barrel shifter even when the barrel shifter is not being used to shift the data, as is often the case. In addition to a loss of power, sending data which will not be shifted through the barrel shifter produces added delay.

There is a need for a low-power, high-performance barrel shifter that will shift a plurality of bits in one clock cycle when desired, but will also pass data through the barrel shifter without delay or loss of power when the data is not to be shifted.

This and other needs are met by the present invention which provides an arrangement for performing arithmetic operations in a processor. This arrangement includes an arithmetic logic unit and a barrel shifter. The arithmetic logic unit (ALU) performs arithmetic operations on data provided as input to the ALU. The ALU has an input for receiving the data and an ALU output at which M-bit results of the arithmetic operations on the data are produced. The barrel shifter includes a barrel shifter input connected to the ALU output, and a shift circuit connected to the barrel shifter input. The shift circuit selectively shifts the M-bit results and produces shifted M-bit results at a shift circuit output.

A barrel shifter output is coupled to the shift circuit output. Shifted M-bit results are produced at the barrel shifter output when the shift circuit is selected to shift the M-bit results.

Unshifted M-bit results are produced at the barrel shifter output when the shift circuit is selected not to shift the M-bit results. The barrel shifter input includes an isolation circuit that isolates the shift circuit from the ALU output when the shift circuit is selected not to shift the M-bit results.

The isolation circuit of the present invention reduces the consumption of power since the shift circuit is isolated when no shifting is required. The highly capacitive nodes in the shift circuit are therefore not switched when the shift circuit is not used to shift the results from the ALU.

In certain preferred embodiments of the invention, the barrel shifter input includes tristate buffers that receive as input the M-bit results from the ALU. The outputs of the tristate buffers are connected to the input of the shift circuit. When the tristate buffers are enabled, and a shift by the shift circuit is desired, the tristate buffers pass the M-bit results to be shifted into the shift circuit. When the M-bit results are not to be shifted, however, a signal causes the tristate buffers' outputs to float. This effectively isolates the shift circuit from the ALU output when the shift circuit is not to shift the M-bit results. Power consumption by the shift circuit is reduced since the internal signal nodes with high capacitance are prevented from being switched due to the floated outputs of the tristate buffers.

An especially low-power embodiment of the present invention provides an isolation circuit that includes an input multiplexer that has a plurality of tristate buffers. A first one of these tristate buffers has an input coupled to receive all M-bits of the M-bit results from the ALU output, and an output at which the M-bits of the M-bit results are produced as a function of the shift control signal, this output being coupled to the shift circuit.

The input multiplexer also has a second tristate buffer having an input coupled to receive the (M-P) most significant bits of the M-bit results, and P bits set at a logical zero, where P is less than M, to form a P-left-shifted-bit results.

By providing a multiplexer at the input, which chooses between a zero-shifted M-bit result to be input to the shift circuit, or an M-bit result that has already been shifted by P bits to be input to the shift circuit, the number of multiplexers used in the shift circuit can be reduced by one-half thus reducing the capacitance of the switch circuit by approximately half. This reduces the power consumption by approximately one-half when the shift circuit is switched. Another feature provided by certain preferred embodiments of the present invention is the integration of the output multiplexer of the barrel shifter within the shift circuit. This integration reduces the delay from the input to the output.

The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

#### Role of barrel shifter in array processing

This invention relates to a system for storing and processing an array of data-elements, such as pixel data.

In particular, the invention is concerned with such a system which comprises a memory having a plurality of memory locations each having a capacity of a predetermined number B (e.g. 32) bits and a processing means for processing data elements and operable to read the data-elements from and/or write the data elements to the memory. Although the memory and processing means are capable of dealing with the predetermined number B of bits (e.g. 32), in some applications, the data-elements may have a lesser resolution (e.g. 16 or 8 bits). In such cases, it would be possible to use only 16 or 8 bits of the 32 bits available for each data-element. However, the memory would not then be used to its full capacity. Also, in a demand-paged dual memory system which pages are swapped from a paging memory into the first-mentioned memory, pages of data-elements would need to be swapped more often than is necessary.

It may therefore be considered expedient to split the whole memory into two for 16-bit data, or four for 8-bit data, and thus overlay whole sub-arrays of the data-elements one on top of another. This would make available the whole capacity of the memory, but would suffer from the disadvantage that severe complications would arise when swapping, for example, just one page of 16-bit or 8-bit data between the memory and paging memory, because it would be necessary to select only half or a quarter of the stored data at each memory location for transfer from the memory to the paging memory, and it would be necessary to mask off half or three-quarters of the memory when transferring a page of data from the paging memory to the first memory.

In order to overcome this problem, in accordance with the invention, the processing means is operable in a mode for processing data-elements having a predetermined number b (e.g. 16) bits not greater than half of said predetermined number B and being operable to read the data-elements from and/or write the data elements to different bit levels (e.g. L(0), L(1)) of the memory locations so that a plurality of data-elements can be stored at such a memory location and so that at no memory location is there stored data-elements from more than one page.

In one embodiment, data elements which are adjacent in at least one direction in the dataarray are stored at different bit levels in the memory. However, in a preferred embodiment, the dataelements are stored in the memory in aligned groups of N (e.g. 16) data-elements, and data elements of groups which are adjacent in at least one direction in the data-array are stored at different bit levels in the memory. In this case, in one arrangement, each memory location is divided into two, that is to say, the number b (e.g. 16) of bits of a data-element is half of the number B (e.g. 32) of bits of a memory location, and the data-elements are arranged in patches each of two groups with the dataelements of the two groups being stored at two respective different bit levels (e.g. bits 0-15, bits 16-31). In another arrangement, each memory location is divided into four, that is to say the number b (e.g. 8) of bits of a data-element is a quarter of the number B (e.g. 32) of bits of a memory location, and the data-elements are arranged in patches of four groups with the pixels of the four groups being stored at four respective different bit levels (e.g. bits 0-7, bits 8-15) Preferably, the system is operable in at least two modes selected from the divided-into-two mode, the divided-into-four mode, and a mode in which all B of the bits at a memory location are used to stored each data-element. In this case, the memory may be addressed by an address having bits whose significance varies in accordance with the selected mode of operation, and the system may further comprise a funnel shifter which receives the address bits whose significance can change and a mode selection signal and which outputs address bits appropriate to the selected mode and a level signal indicative of the bit level in the memory of the data-element to be accessed.

During reading of the memory the processing means may be operable to read all of the data at a memory location, the system further comprising means for supplying a shift signal dependent on the level signal to the processing means and the processing means may be operable to bit-shift the read data by an amount dependent on the shift signal to that the data-element to be processed occupies predetermined bit positions.

During writing to the memory, in at least said first-mentioned mode the processing means is preferably operable to duplicate the bits to be written at the different levels and the system may comprise means for supplying a partial write-enable signal dependent on the level signal for controlling the memory so that the data-element is written only to the appropriate bit levels of the memory. In the preferred embodiment, the processing means comprises a plural number N (e.g. 16) of processors equal in number N to the number of data-elements in a group, where the processors are capable of accessing in parallel all of the data-elements of a group. In this case upon reading of a group which is misaligned with respect to an aligned group, the shift signal supplying means is preferably operable to supply to the processors a respective shift signal for each data-element in the misaligned group which is dependent upon the position of the data-element in the group and the misalignment of the group.

Also, upon writing of a group which is misaligned with respect to an aligned group, the partial write-enable signal supplying means is preferably operable to supply to the memory a respective partial write-enable signal for each data-element in the misaligned group which is dependent on the position of the data-element in the group and the misalignment of the group.

# <u>CHAPTER – 3</u> <u>AN INTRODUCTION TO XILINX 9.1i</u>

The ISE 9.1i provides Xilinx PLD designers with the basic design process using ISE 9.1i. In this chapter you will understande of how to create, verify, and implement a design.

This chapter contains the following sections:

- "Getting Started"

- "Create a New Project"

- "Create an HDL Source"

- "Design Simulation"

- "Create Timing Constraints"

- "Implement Design and Verify Constraints"

- "Reimplement Design and Verify Pin Locations"

- "Download Design to the Spartan<sup>™</sup>-3 Demo Board"

## **3.1 Getting Started**

Software Requirements:- ISE 9.1i

Hardware Requirements:- Spartan-3 Startup Kit, containing the Spartan-3 Startup Kit Demo Board.

Starting the ISE Software To start ISE, double-click the desktop icon,

or start ISE from the Start menu by selecting:

- Start

- All Programs

- Xilinx ISE 9.1i

- Project Navigator

*Note:* Your start-up path is set during the installation process and may differ from the one above. Accessing Help

At any time during the tutorial, you can access online help for additional information about the ISE software and related tools.

To open Help, do either of the following:

- Press F1 to view Help for the specific tool or function that you have selected orhighlighted.

- Launch the **ISE Help Contents** from the Help menu. It contains information about creating and maintaining your complete design flow in ISE.

| File Edit '    | View Project | Source | Process | Window | Help                                                                                     |          |

|----------------|--------------|--------|---------|--------|------------------------------------------------------------------------------------------|----------|

| I 🖸 🖸 🛛        | 303          | ØĨ     | 80      | () a   | Help Topics                                                                              | N?       |

| <b>. X</b> 🖻 ( | 9 9 9 G      | A 😹    |         |        | Software Manuals<br>Xilinx on the Web<br>Tutorials<br>Tip of the Day<br>Software Updates | <b>S</b> |

Figure 1: ISE Help Topics

## **3.2 Create a New Project**

Create a new ISE project which will target the FPGA device on the Spartan-3 Startup Kit demo board.

To create a new project:

Select File

New Project... The New Project Wizard appears.

- 2. Type **tutorial** in the Project Name field.

- 3. Enter or browse to a location (directory path) for the new project. A tutorial subdirectory is created automatically.

- 4. Verify that HDL is selected from the Top-Level Source Type list.

- 5. Click Next to move to the device properties page

- 6. Fill in the properties in the table as shown below:

- Product Category: All

- Family: Spartan3

- Device: XC3S200

- Package: FT256

- Speed Grade: -4

- Top-Level Source Type: HDL

- Synthesis Tool: XST (VHDL/Verilog)

- Simulator: ISE Simulator (VHDL/Verilog)

- Preferred Language: VHDL (or Verilog)

- Verify that Enable Enhanced Design Summary is selected.

Leave the default values in the remaining fields.

When the table is complete, your project properties will look like the following:

| Property Name                  | Value                        |   |

|--------------------------------|------------------------------|---|

| Product Category               | General Purpose              | ~ |

| Family                         | Spartan3E                    | ~ |

| Device                         | ×C3S500E                     | ~ |

| Package                        | FG320                        | ~ |

| Speed                          | -4                           | ~ |

| Top-Level Source Type          | HDL                          | Y |

| Synthesis Tool                 | XST (VHDL/Verilog)           | ~ |

| Simulator                      | ISE Simulator (VHDL/Verilog) | ~ |

| Preferred Language             | VHDL                         | ~ |

| Enable Enhanced Design Summary |                              |   |

| Enable Message Filtering       |                              |   |

| Display Incremental Messages   |                              |   |

7. Click **Next** to proceed to the Create New Source window in the New Project Wizard. At the end of the next section, your new project will be complete.

## **<u>3.3 Create an HDL Source</u>**

In this section, you will create the top-level HDL file for your design. Determine the language that you wish to use for the tutorial. Then, continue either to the "Creating a VHDL Source" section below, or skip to the "Creating a Verilog Source" section.

Creating a VHDL Source

Create a VHDL source file for the project as follows:

- 1. Click the New Source button in the New Project Wizard.

- 2. Select VHDL Module as the source type.

- 3. Type in the file name **counter**.

- 4. Verify that the Add to project checkbox is selected.

- 5. Click Next.

6. Declare the ports for the counter design by filling in the port information as shown below:

| Enlit, Name co                | unter     |            |     |    |       |  |  |

|-------------------------------|-----------|------------|-----|----|-------|--|--|

| Architecture Name Eal avioral |           |            |     |    |       |  |  |

| Part Nome                     | E rection | Fue        | 493 | 33 |       |  |  |

| ILOIN                         | n         | ¥ 🗆        | 1   |    | 11.21 |  |  |

| DINECT ON                     | n         | <b>∽</b> □ |     |    |       |  |  |

| COUNT_OUT                     | Jul       | - E        |     | 3  | 0     |  |  |

|                               | n         | × 🗆        |     |    |       |  |  |

|                               | n         | × 🗌        |     |    |       |  |  |

|                               | n         | <u>~</u> ] |     |    |       |  |  |

|                               | n         | × 🗆        |     |    |       |  |  |

|                               | n         | <b>X</b>   |     |    | -     |  |  |

|                               | n         | ~          |     |    |       |  |  |

|                               | n         | × 🗆        |     |    | 8     |  |  |

Figure 3: Define Module

7. Click **Next**, then **Finish** in the New Source Wizard - Summary dialog box to complete the new source file template.

8. Click Next, then Next, then Finish.

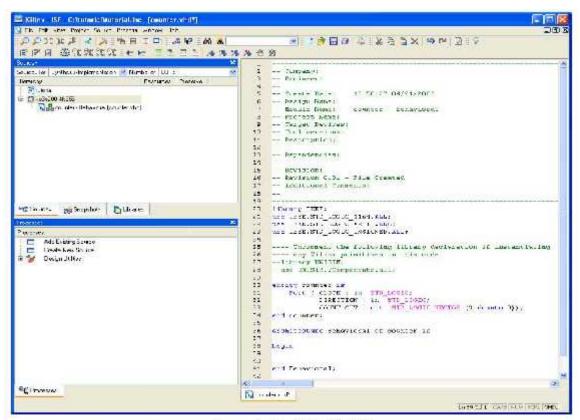

The source file containing the entity/architecture pair displays in the workspace, and the counter displays in the Source tab, as shown below:

Ligure d: New Project in ISE

Using Language Templates (VHDL)

The next step in creating the new source is to add the behavioral description for the counter. To do this you will use a simple counter code example from the ISE Language templates and customize it for the counter design.

- 1. Place the cursor just below the begin statement within the counter architecture.

- 2. Open the Language Templates by selecting Edit

- Language Templates...

*Note:* You can tile the Language Templates and the counter file by selecting **Window**

• Tile Vertically to make them both visible.

3. Using the "+" symbol, browse to the following code example:

#### VHDL

- Synthesis Constructs

- Coding Examples

- Counters

- Binary

- Up/Down Counters

- Simple Counter

- 1. With Simple Counter selected, select Edit

- 2. Use in File, or select the Use Template in File toolbar button. This step copies the template into the counter source file.

- 4. Close the Language Templates.

#### Final Editing of the VHDL Source:

- Add the following signal declaration to handle the feedback of the counter output below the architecture declaration and above the first begin statement: signal count int : std logic vector(3 downto 0) :"0000";

- 2. Customize the source file for the counter design by replacing the port and signal name placeholders with the actual ones as follows:

- replace all occurrences of <clock> with CLOCK

- replace all occurrences of <count\_direction> with DIRECTION

- replace all occurrences of <count> with count\_int

- 3. Add the following line below the end process; statement:

- COUNT\_OUT <= count\_int;

- 4. Save the file by selecting **File Save**.

When you are finished, the counter source file will look like the following:

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitive in this code. --library UNISIM; --use UNISIM.VComponents.all; entity counter is Port ( CLOCK : in STD\_LOGIC; DIRECTION : in STD\_LOGIC; COUNT\_OUT : out STD\_LOGIC\_VECTOR (3 downto 0)); end counter;

```

architecture Behavioral of counter is

signal count_int : std_logic_vector(3 downto 0) := "0000";

begin

process (CLOCK)

begin

if CLOCK='1' and CLOCK'event then

if DIRECTION='1' then

count_int <= count_int + 1;

else

count_int <= count_int + 1;

end if;

end if;

end if;

end process;

COUNT_OUT <= count_int;

end Behavioral;

```

You have now created the VHDL source for the tutorial project. Skip past the Verilog sections below, and proceed to the "Checking the Syntax of the New Counter Module" section.

Checking the Syntax of the New Counter Module

When the source files are complete, check the syntax of the design to find errors and types.

- 1. Verify that **Synthesis/Implementation** is selected from the dropdown list in the Sources window.

- 2. Select the **counter** design source in the Sources window to display the related processes in the Processes window.

- 3. Click the "+" next to the Synthesize-XST process to expand the process group.

- 4. Double-click the Check Syntax process.

*Note:* You must correct any errors found in your source files. You can check for errors in the Console tab of the Transcript window. If you continue without valid syntax, you will not be able to simulate or synthesize your design.

5. Close the HDL file.

## 3.4 Design Simulation

Verifying Functionality using Behavioral Simulation

Create a test bench waveform containing input stimulus you can use to verify the functionality of the counter module. The test bench waveform is a graphical view of a test bench.

Create the test bench waveform as follows:

1. Select the **counter** HDL file in the Sources window.

2. Create a new test bench source by selecting **Project New Source**.

3. In the New Source Wizard, select **Test Bench WaveForm** as the source type, and type **counter tbw** in the File Name field.

4. Click Next.

5. The Associated Source page shows that you are associating the test bench waveform with the source file counter. Click **Next**.

6. The Summary page shows that the source will be added to the project, and it displays the source directory, type and name. Click **Finish**.

7. You need to set the clock frequency, setup time and output delay times in the Initialize Timing dialog box before the test bench waveform editing window opens.

The requirements for this design are the following:

- The counter must operate correctly with an input clock frequency = 25 MHz.

- The DIRECTION input will be valid 10 ns before the rising edge of CLOCK.

- The output (COUNT\_OUT) must be valid 10 ns after the rising edge of CLOCK.

The design requirements correspond with the values below.

Fill in the fields in the Initialize Timing dialog box with the following information:

- Clock High Time: **20** ns.

- Clock Low Time: **20** ns.

- Input Setup Time: **10** ns.

- Output Valid Delay: **10** ns.

- Offset: **0** ns.

- Global Signals: GSR (FPGA)

Note: When GSR(FPGA) is enabled, 100 ns. is added to the Offset value automatically.

• Initial Length of Test Bench: **1500** ns.

Leave the default values in the remaining fields.

|                                                                                              | A<br>Maximum ,<br>output delay | :<br>UR <mark>_</mark> | Minimum<br>minimum<br>satup<br>Cluck<br>low for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------------------------------------------------------------------------------------------|--------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Cleal: Timing Inform                                                                         | ntion                          | 19                     | Clock Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Inputs are assigned at "Input Setup Time" and<br>outputs are checked at "Output Vald Delay". |                                |                        | Single Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Rising Edge     O Faling Ecge                                                                |                                |                        | O Multiple Llocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 🕐 Dual Edge (DD                                                                              |                                |                        | <ul> <li>Contributorial (or internal clock)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Clock High Time                                                                              | 20                             | na                     | Combinatorial Timing Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Clock Low Inne                                                                               | 20                             | 16                     | Input: ere assigned, outputs are decoded then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Input Setup Time                                                                             | 10                             | Ins                    | <ul> <li>checked. A celap between inputy and outputs avoids<br/>assignment/checking conflicts.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Output Valid Delay                                                                           | 10                             | ns                     | Check Unipuls Ltd Inst After Ir puts are Assigned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Diffset                                                                                      | 100                            | na                     | Assign Liquits [b1] is Atter Hubits are Liberke                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Global Signals                                                                               |                                |                        | to de the sector de la constance de |  |

| ाणा व्याप्यान्य                                                                              | 🔽 LEITHEAL                     |                        | Initial ength of Lest Dencat [5 II n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| High for Initial: 100 os                                                                     |                                |                        | Time Scale: ns 🛛 💌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

Figure 7: Initialize Timing

- 8. Click Finish to complete the timing initialization.

- 9. The blue shaded areas that precede the rising edge of the CLOCK correspond to the Input Setup Time in the Initialize Timing dialog box. Toggle the DIRECTION port to define the input stimulus for the counter design as follows:

- Click on the blue cell at approximately the **300** ns to assert DIRECTION high so that the counter will count up.

- Click on the blue cell at approximately the **900** ns to assert DIRECTION low so that the counter will count down.

*Note:* For more accurate alignment, you can use the **Zoom In** and **Zoom Out** toolbar buttons.

| 🛛 Xilinx - 15E - C:Xu | ioria Mur | torial.ise - [counter_tbw]                        |          |

|-----------------------|-----------|---------------------------------------------------|----------|

| Be Fil Sis Frij       | al Schuis | Printes Tel Real Franchise Marines Hall           | 360      |

|                       |           | ■ 2 後洋洋洋洋 2 2 2 1 2 1 2 1 2 1 2 1 2 2 2 3 2 3 2 3 | M        |

| End Time:<br>1500 ns  |           | `2015 2C3r∋ 440r∋ €3C15 7€3ns 523r∋ 1000ns `240r  | s 140Cns |

| Land Charles          | 0         |                                                   |          |

| DIRECT OF             | 0         |                                                   |          |

| п 📷 солят сл.,        | 0 (       | 0                                                 |          |

Figure 8: Test Bench Waveform

10. Save the waveform.

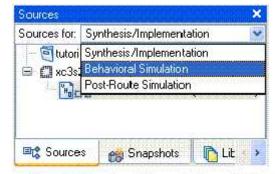

11. In the Sources window, select the **Behavioral Simulation** view to see that the test bench waveform file is automatically added to your project.

Figure 9: Behavior Simulation Selection

12. Close the test bench waveform.

## **3.5 Simulating Design Functionality**

Verify that the counter design functions as you expect by performing behavior simulation as follows:

- Verify that Behavioral Simulation and counter\_tbw are selected in the Sources window.

- In the Processes tab, click the "+" to expand the Xilinx ISE Simulator process and double-click the Simulate Behavioral Model process. The ISE Simulator opens and runs the simulation to the end of the test bench.

- 3. To view your simulation results, select the **Simulation** tab and zoom in on the transitions.

The simulation waveform results will look like the following:

| D2 目前 3 日 日 了 三 際 洗洗洗洗 為 3 み 1 3 1 1 2 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Now:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1540 ns 2) rs 328 319 rs 827 1232 16 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 30 etwek () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () () ( |

| 🖁 dhetdon C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| □ ③( court_out) 01 = 12 - ( = 0 - 対応 (法保留) (項目的) (対応) (対応) (注意) ((法定) (法定) ((法定) ((法定) ((法定) ((法定) ((法定) ((法定) ((法定) ((法定) ((法定) (((法定) ((((((((((                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Figure 10: Simulation Results

Note: You can ignore any rows that start with TX.

- 4. Verify that the counter is counting up and down as expected.

- 5. Close the simulation view. If you are prompted with the following message, "You have an active simulation open. Are you sure you want to close it?", click Yes to continue. You have now completed simulation of your design using the ISE Simulator.

## **3.6 Create Timing Constraints**

Specify the timing between the FPGA and its surrounding logic as well as the frequency the design must operate at internal to the FPGA. The timing is specified by entering constraints that guide the placement and routing of the design. It is recommended that you enter global constraints. The clock period constraint specifies the clock frequency at which your design must operate inside the FPGA. The offset constraints specify when to expect valid data at the FPGA inputs and when valid data will be available at the FPGA outputs.

## **3.6.1 Entering Timing Constraints**

To constrain the design do the following:

- 1. Select **Synthesis/Implementation** from the drop-down list in the Sources window.

- 2. Select the **counter** HDL source file.

- Click the "+" sign next to the User Constraints processes group, and double-click the

**Create Timing Constraints** process.ISE runs the Synthesis and Translate steps and automatically creates a User Constraints File (UCF). You will be prompted with the following message:

| Ргој | ect Navigator                                                                                                                                                                                                                                                                                                                                                                  |